3月17日消息,三星电子代表宋在旭在2月举行的IEEE ISSCC 2025全体会议上发表演讲,分享了对高带宽内存(HBM)未来技术演进的展望。他提出了两种主要的技术方向:通过定制版本优化HBM设计以减少I/O面积占用,以及在基础芯片中直接集成加速器单元。

定制版HBM

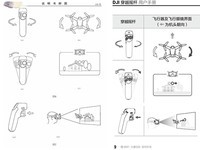

当前的HBM内存架构在xPU处理器与HBM基础裸片(Base Die)之间通过数千个PHY I/O进行互联。而定制版HBM则采用了更高效率的D2D(Die-to-Die)裸片间互联技术。这一改进不仅缩短了两芯片之间的间距,还减少了所需的I/O数量,从而显著提升了能效表现。

此外,D2D互联方案的面积占用相比现有技术更低,为xPU和Base Die中容纳更多芯片IP提供了空间支持。值得注意的是,在定制版HBM架构中,LPDDR控制器/PHY和HBM控制器从xPU芯片转移至HBM Base Die中,进一步优化了系统架构。

3D集成HBM

目前,HBM内存与处理器采用的是2.5D封装技术,但在这一结构下,HBM的大部分功耗被浪费在数据搬运过程中。为了改善这一点,未来的HBM有望采用3D集成方案,即将加速器单元直接内置到基础芯片中。在这种设计中,加速器通过TSV(硅通孔)技术与DRAM芯片实现直连,省去了现有架构中复杂的中介层,从而显著提高了数据传输的能效。

相关资料显示,某些厂商已经推出类似定制HBM计算架构的产品,其中XPU与HBM之间的I/O接口得到了进一步优化,体积更小但性能更强。

本文属于原创文章,如若转载,请注明来源:三星展望HBM未来:定制版与3D集成两大方向https://dcdv.zol.com.cn/961/9612650.html